- 您现在的位置:买卖IC网 > Sheet目录342 > MCB1114 (Keil)BOARD EVALUATION FOR NXP LPC1114

NXP Semiconductors

10.4 I 2 C-bus

Table 13. Dynamic characteristic: I 2 C-bus pins (Fast-mode Plus)

T amb = ? 40 ° C to +85 ° C; V DD(3V3) = V DD(IO) = 3.3 V. [1][2][3]

LPC1111/12/13/14

Symbol

f SCL

t f

t SU;DAT

Parameter

SCL clock frequency

fall time

data set-up time

Conditions

-

Min

-

-

50

Typ

-

-

-

Max

1

45

-

Unit

MHz

ns

ns

[1]

[2]

[3]

Parameters are valid over operating temperature range unless otherwise specified.

Main clock frequency 10 MHz; system clock divider AHBCLKDIV = 0x1; I 2 C-bus interface configured in master mode.

Bus capacitance C b = 550 pF; external pull-up resistance of 103 Ω .

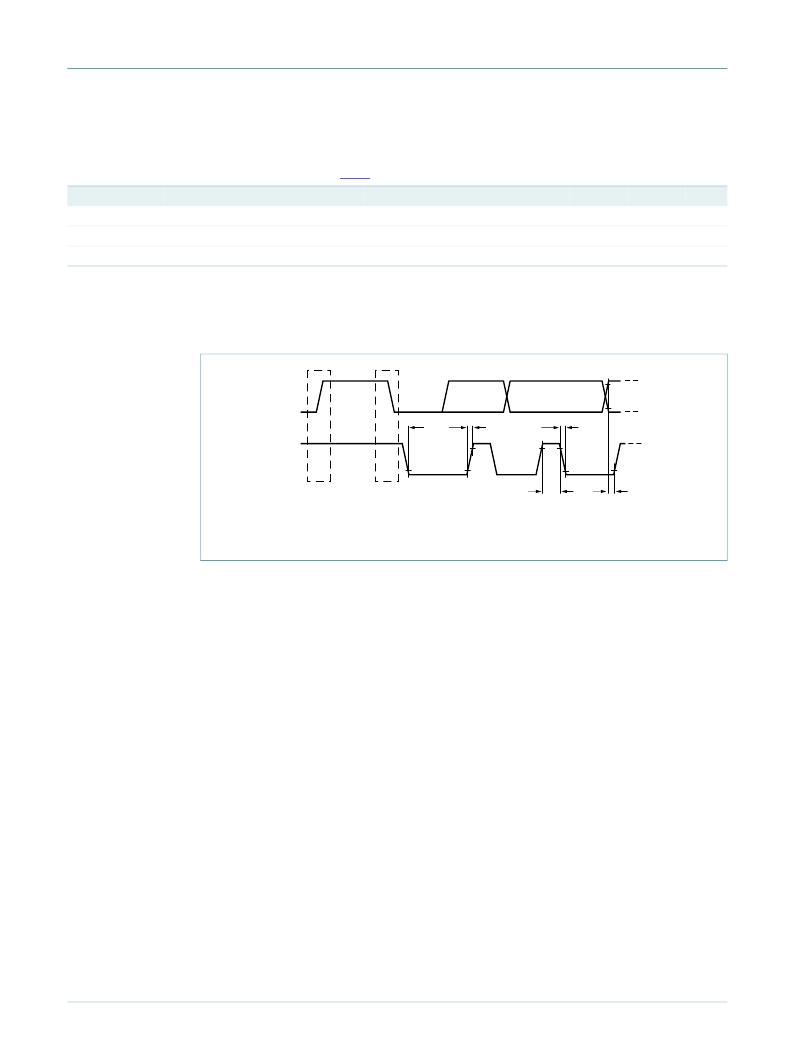

SDA

SCL

P

S

t LOW

t r

t HIGH

t f

t SU;DAT

002aae860

Fig 20. I 2 C-bus pins clock timing

LPC1111_12_13_14_0

? NXP B.V. 2009. All rights reserved.

Objective data sheet

Rev. 00.11 — 13 November 2009

41 of 53

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MCB11C14

BOARD EVAL FOR NXP LPC11C14

MCB2470

BOARD EVAL NXP LPC247X SERIES

MCBSTM32EXL

BOARD EVALUATION FOR STM32F103ZE

MCBTMPM330

BOARD EVAL TOSHIBA TMPM330 SER

MCIMX25WPDKJ

KIT DEVELOPMENT WINCE IMX25

MCIMX53-START-R

KIT DEVELOPMENT I.MX53

MCM69C432TQ20

IC CAM 1MB 50MHZ 100LQFP

MCP1401T-E/OT

IC MOSFET DRVR INV 500MA SOT23-5

相关代理商/技术参数

MCB1114-ED

制造商:ARM Ltd 功能描述:KEIL NXP LPC1114 EVAL BOARD

MCB1114U

功能描述:开发板和工具包 - ARM EVAL BOARD FOR NXP LPC1114 + ULINK2

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCB1114U-ED

制造商:ARM Ltd 功能描述:KEIL NXP LPC1114 EVAL BOARD

MCB1114UME

功能描述:开发板和工具包 - ARM EVAL BOARD FOR NXP LPC1114 + ULINK-ME

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCB1114UME-ED

制造商:ARM Ltd 功能描述:KEIL NXP LPC1114 EVAL BOARD

MCB11C14

功能描述:开发板和工具包 - ARM EVAL BOARD FOR NXP LPC11C14

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCB11C14-ED

制造商:ARM Ltd 功能描述:KEIL NXP LPC11C14 EVAL BOARD

MCB11C14U

功能描述:开发板和工具包 - ARM EVAL BOARD FOR NXP LPC11C14 + ULINK2

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V